锁相环设计中的VCXO Oscillator性能权衡

许多VCXOs是低带宽PLL的关键组件.这种PLL通常用于电信、视频、音频、网络和仪器仪表应用中的同步和/或抖动清除.本应用笔记描述了锁相环设计中关键VCXO石英晶体振荡器特定性能参数之间的关系及其权衡.

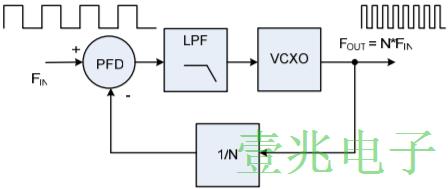

基本锁相环架构

图1显示了一个简单的锁相环框图.基准时钟提供输入频率FIN.

鉴频鉴相器比较输入时钟和输出时钟的相位,并基于相位差产生周期性误差信号.该周期性信号通过环路滤波器进行低通滤波,并作为模拟控制电压传递给VCXO输入端.VCXO输出频率由控制输入电压控制,并与其大致成比例.输出频率将随着控制电压的变化而变化,直到产生的相位误差能量被驱动为零.在上面所示的常见情况下,VCXO石英晶振产生的输出频率和反馈给功率因数校正的频率之间存在一个分频比.这导致参考频率的有效乘以N.

PLL作为频率跟踪器/滤波器

只要变化速度在锁相环滤波器的总带宽内,锁相环输出就会跟踪参考频率的变化.它还平滑或过滤输入参考频率中的高频变化或抖动.这是一个将锁相环用作“抖动清除器”的例子——跟踪参考时钟的低频变化,例如在网络同步应用中,同时滤除高频抖动.这里的一个权衡是,VCXO压控贴片振荡器本身中的低频偏移相位噪声也被衰减,高频偏移VCXO相位噪声被传递到输出端.同样的环路在这样的设计中,为几个相互冲突的目标选择环路带宽需要权衡:

1)衰减参考输入噪声(带宽越低越好)

2)跟踪参考变化达到所需带宽(更高的跟踪速度要求意味着更高的带宽)

3)衰减VCXO产生的噪声(带宽越高越好).

前两个目标相当于低通滤波器中通常的权衡:跟踪性能与噪声滤波性能.一般来说,使用较低噪声的VCXO可以简化这两个参数的权衡,因为衰减VCXO压控晶体振荡器产生的噪声不太重要.锁相环系统中的VCXO通常可以建模为简单增益Kv[1].与任何反馈系统一样,闭环动态将是该增益的函数,并且可能由于Kv选择不当而变得不稳定.因此,Kv是回路设计中更关键的选择之一.Kv的合适范围通常由应用要求决定,并受满足这些要求的VCXO器件可用性的限制.

VCXO参数对PLL性能的影响

在PLL设计中,需要最小的Kv和最大APR.但是,使用基于Quartz的VCXO很难同时获得这两者.本节描述了APR和Kv之间的权衡,并解释了SiTime硅晶振公司的VCXO如何减轻设计人员进行这种权衡.

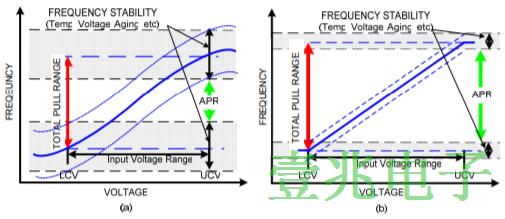

绝对拉力范围

由于PLL设计人员通常关注在所有条件下跟踪指定范围的输入频率,因此绝对拉动范围(APR)[1]是PLL设计的更相关规范.图1显示了典型石英VCXO和SiTimeVCXO的频率与电压(FV)特性.灰色条带表示FV特性可以随条件变化多远,并证明标称或总拉伸范围与APR之间的差异.APR必须大于最大预期参考频率变化.否则,PLL可能无法跟踪参考输入频率.

对于基于石英的VCXO,为了获得更高的APR,通常需要使用低Q晶体以使晶体更“可拉”.然而,这也具有降低频率稳定性的效果.因此,必须在应用程序所需的最小APR与该APR可用的最小频率稳定性之间进行权衡.通常,最好选择满足应用要求的最低APR.

SiTime VCXO对绝对拉动范围的益处

由于较高的拉动范围VCXO通常意味着更大(更差)的频率稳定性,因此选择标称拉动范围明显大于其他要求的VCXO并不罕见,只是为了提供足够高的APR以满足最低应用要求.这通常要求VCXO具有更陡峭的FV特性,这会对PLL设计中的噪声和稳定裕度产生不利影响,从而带来设计损失.

SiTime的VCXO系列不受此影响.由于响应控制电压变化的频率变化是通过VCXO有源晶振器件内的PLL产生的,因此SiTime使频率稳定性与拉动范围本身无关.这允许设计人员精确选择应用程序所需的APR,而不是更多.

图2:典型的VCXOFV特性:(a)典型的QuartzVCXO特性,(b)典型的SiTimeVCXO特性

Kv线性

标准石英基VCXO的Kv[1]可在输入控制电压范围内显着变化,通常为10%至20%.通常,具有更好线性度规格的部件将具有较低的Kv变化,但即使在具有良好线性度规格的部件中也可能具有显着的Kv变化.一些数据表可指定“平均”Kv,但由于Kv影响重要的PLL性能参数,如带宽和相位裕度(稳定性),必须在成功的设计中理解并考虑整个Kv变化.

Kv对PLL设计的影响

对于大多数低带宽PLL,VCXO贴片晶振的FV特性被建模为简单增益Kv.与任何控制系统一样,调整增益将改变闭环动态.在绝大多数情况下,增加Kv将增加环路速度(更好的跟踪),但也会增加过冲和峰值,并可能使闭环系统更接近不稳定性.较高的Kv也会使系统对控制输入端的电压噪声更敏感,从而增加整体系统抖动.

典型的基于石英的VCXO通过变容二极管实现其电压控制功能,这导致弯曲的FV特性,如图3(a)所示.这些器件的线性度规格通常在5%至10%的范围内.这种弯曲特性会导致Kv特性在输入电压控制范围内发生显着变化,如图3(c)所示.为了成功使用这样的VCXO振荡器,PLL设计人员必须考虑最小Kv,这限制了PLL带宽和跟踪能力,以及最大Kv,它决定了最坏情况下的抖动和噪声性能,以及最坏情况下的系统稳定性.

为了复合,线性度和Kv曲线本身可能会随温度和Vdd等条件发生变化,迫使设计人员考虑这些条件对Kv的最坏情况影响.这些依赖关系可能没有在给定的数据表中详细记录,但可能只能在保守的“最小”和“最大”Kv规范中捕获.最后,设计者最初可以在最小APR的基础上选择VCXO晶振系列.因为随着APR越高,VCXO的频率稳定性越差,在相同的电压控制范围内实现相同的APR需要更高的Kv.这意味着可能需要选择显着高于系统性能和环路稳定性所需的Kv,以满足APR规范!

“推荐阅读”

相关技术支持

- Suntsu松图Wi-Fi传感精确度的核心基础与技术赋能

- RL78/F25微控制器赋能下一代电子/电气架构筑牢智能控制核心基石

- Pletronics低功耗SM2245KE-32.768K-T3K晶体振荡器的精度和功率效率

- ACT艾西迪SY00003GIHD‐PF晶体术语的A到Z技术论文

- CRYSTEK振荡器CCPD-575X-20-80.000晶体负载计算

- LV-PECL石英晶振,LV-LVDS晶振,LV-PECL振荡器,LVDS-HCSL普通有源晶振贴片四脚/而差分有源晶振则是贴片六脚

- 泰艺开发的压控温补振荡器VC-TCXO,适合用于手机TXEADCSANF-26.000000

- Abracon晶振开发AX5系列的有源振荡器AX5PAF1-26.00000,支持差分输出

- 晶振输出逻辑对频率有什么影响,又怎样尽可能降低抖动?

- 为什么晶振会出现频偏,用什么方法可以最大化缩小其影响